PCB 16 lớp mang lại sự phức tạp và linh hoạt theo yêu cầu của các thiết bị điện tử hiện đại. Thiết kế khéo léo và lựa chọn trình tự xếp chồng cũng như phương pháp kết nối giữa các lớp là rất quan trọng để đạt được hiệu suất bo mạch tối ưu. Trong bài viết này, chúng ta sẽ khám phá những cân nhắc, hướng dẫn và phương pháp hay nhất để giúp các nhà thiết kế và kỹ sư tạo ra bảng mạch 16 lớp hiệu quả và đáng tin cậy.

1.Tìm hiểu những điều cơ bản về trình tự xếp chồng PCB 16 lớp

1.1 Định nghĩa và mục đích của xếp hàng

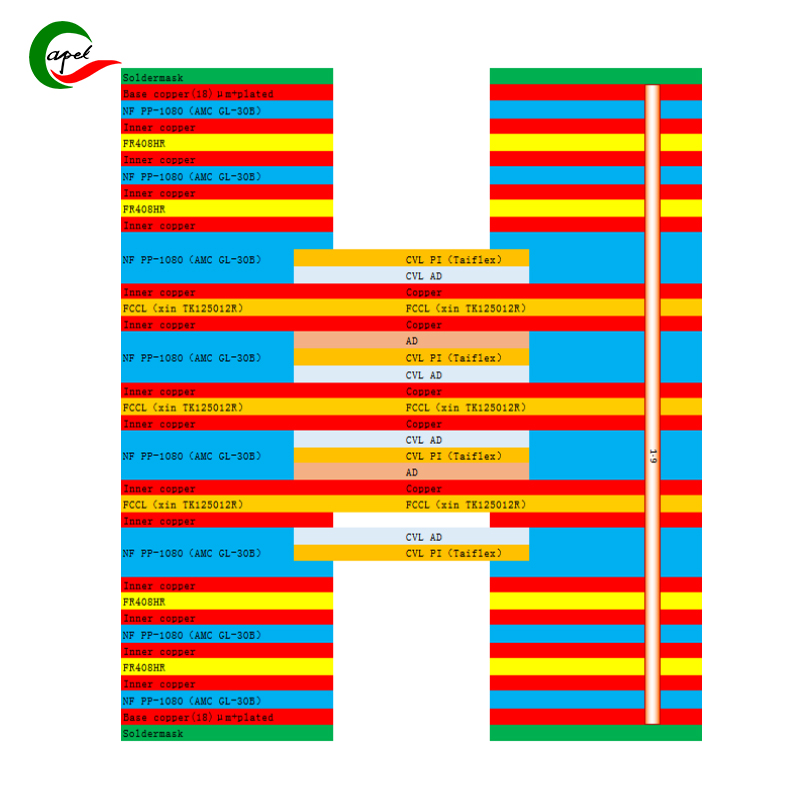

Trình tự xếp chồng đề cập đến sự sắp xếp và thứ tự trong đó các vật liệu như đồng và lớp cách điện được ghép lại với nhau để tạo thành một bảng mạch nhiều lớp. Trình tự xếp chồng xác định vị trí của các lớp tín hiệu, lớp nguồn, lớp nối đất và các thành phần quan trọng khác trong ngăn xếp.

Mục đích chính của trình tự xếp chồng là đạt được các đặc tính cơ và điện cần thiết của bo mạch. Nó đóng một vai trò quan trọng trong việc xác định trở kháng của bảng mạch, tính toàn vẹn tín hiệu, phân phối điện, quản lý nhiệt và tính khả thi trong sản xuất. Trình tự xếp chồng cũng ảnh hưởng đến hiệu suất tổng thể, độ tin cậy và khả năng sản xuất của bo mạch.

1.2 Các yếu tố ảnh hưởng đến thiết kế trình tự xếp chồng: Có một số yếu tố cần xem xét khi thiết kế trình tự xếp chồng của một

PCB 16 lớp:

a) Các cân nhắc về điện:Việc bố trí các mặt phẳng tín hiệu, nguồn và mặt đất phải được tối ưu hóa để đảm bảo tính toàn vẹn tín hiệu phù hợp, kiểm soát trở kháng và giảm nhiễu điện từ.

b) Các cân nhắc về nhiệt:Việc bố trí các mặt phẳng nguồn và mặt đất cũng như bao gồm các lỗ tản nhiệt giúp tản nhiệt hiệu quả và duy trì nhiệt độ hoạt động tối ưu của bộ phận.

c) Hạn chế trong sản xuất:Trình tự xếp chồng được chọn phải tính đến khả năng và hạn chế của quy trình sản xuất PCB, chẳng hạn như tính sẵn có của vật liệu, số lớp, tỷ lệ khung hình khoan,và độ chính xác căn chỉnh.

d) Tối ưu hóa chi phí:Việc lựa chọn vật liệu, số lớp và độ phức tạp khi xếp chồng phải phù hợp với ngân sách dự án đồng thời đảm bảo hiệu suất và độ tin cậy cần thiết.

1.3 Các loại trình tự xếp chồng bảng mạch 16 lớp phổ biến: Có một số trình tự xếp chồng phổ biến cho bảng mạch 16 lớp

PCB, tùy thuộc vào hiệu suất và yêu cầu mong muốn. Một số ví dụ phổ biến bao gồm:

a) Trình tự xếp chồng đối xứng:Trình tự này bao gồm việc đặt các lớp tín hiệu đối xứng giữa lớp nguồn và lớp đất để đạt được tính toàn vẹn tín hiệu tốt, nhiễu xuyên âm tối thiểu và tản nhiệt cân bằng.

b) Trình tự xếp chồng tuần tự:Trong chuỗi này, các lớp tín hiệu được sắp xếp tuần tự giữa lớp nguồn và lớp đất. Nó cung cấp khả năng kiểm soát tốt hơn đối với việc sắp xếp lớp và có lợi cho việc đáp ứng các yêu cầu về tính toàn vẹn tín hiệu cụ thể.

c) Thứ tự xếp hỗn hợp:Điều này liên quan đến sự kết hợp của các thứ tự xếp chồng đối xứng và tuần tự. Nó cho phép tùy chỉnh và tối ưu hóa bố cục cho các phần cụ thể của bảng.

d) Trình tự xếp chồng nhạy cảm với tín hiệu:Trình tự này đặt các lớp tín hiệu nhạy cảm gần mặt phẳng mặt đất hơn để có khả năng chống nhiễu và cách ly tốt hơn.

2. Những cân nhắc chính cho việc lựa chọn trình tự xếp chồng PCB 16 lớp:

2.1 Cân nhắc tính toàn vẹn tín hiệu và tính toàn vẹn nguồn:

Trình tự xếp chồng có tác động đáng kể đến tính toàn vẹn tín hiệu và tính toàn vẹn nguồn của bo mạch. Vị trí thích hợp của tín hiệu và mặt phẳng nguồn/mặt đất là rất quan trọng để giảm thiểu nguy cơ méo tín hiệu, nhiễu và nhiễu điện từ. Những cân nhắc chính bao gồm:

a) Vị trí lớp tín hiệu:Các lớp tín hiệu tốc độ cao phải được đặt gần mặt phẳng mặt đất để cung cấp đường dẫn trở lại có độ tự cảm thấp và giảm thiểu sự ghép nhiễu. Các lớp tín hiệu cũng cần được bố trí cẩn thận để giảm thiểu độ lệch tín hiệu và độ dài phù hợp.

b) Phân bố mặt phẳng điện:Trình tự xếp chồng phải đảm bảo phân bổ mặt phẳng công suất phù hợp để hỗ trợ tính toàn vẹn nguồn. Cần bố trí đủ công suất và mặt đất một cách chiến lược để giảm thiểu sụt áp, gián đoạn trở kháng và ghép nhiễu.

c) Tụ tách:Vị trí thích hợp của các tụ tách rời là rất quan trọng để đảm bảo truyền tải điện đầy đủ và giảm thiểu tiếng ồn của nguồn điện. Trình tự xếp chồng phải đảm bảo khoảng cách giữa các tụ điện tách rời với mặt phẳng nguồn và mặt đất.

2.2 Quản lý nhiệt và tản nhiệt:

Quản lý nhiệt hiệu quả là rất quan trọng để đảm bảo độ tin cậy và hiệu suất của bảng mạch. Trình tự xếp chồng phải tính đến việc bố trí thích hợp các mặt phẳng nguồn và mặt đất, các đường dẫn nhiệt và các cơ chế làm mát khác. Những cân nhắc quan trọng bao gồm:

a) Phân bố mặt phẳng công suất:Việc phân bổ đầy đủ nguồn điện và mặt đất trong toàn bộ ngăn xếp giúp truyền nhiệt ra khỏi các bộ phận nhạy cảm và đảm bảo phân bổ nhiệt độ đồng đều trên toàn bo mạch.

b) Đường dẫn nhiệt:Trình tự xếp chồng phải cho phép tản nhiệt hiệu quả thông qua vị trí để tạo điều kiện tản nhiệt từ lớp bên trong sang lớp bên ngoài hoặc tản nhiệt. Điều này giúp ngăn chặn các điểm nóng cục bộ và đảm bảo tản nhiệt hiệu quả.

c) Vị trí thành phần:Trình tự xếp chồng nên xem xét cách sắp xếp và đặt gần các bộ phận làm nóng để tránh quá nhiệt. Việc căn chỉnh phù hợp các bộ phận với cơ chế làm mát như tản nhiệt hoặc quạt cũng cần được xem xét.

2.3 Hạn chế trong sản xuất và tối ưu hóa chi phí:

Trình tự xếp chồng phải tính đến các hạn chế trong sản xuất và tối ưu hóa chi phí, vì chúng đóng vai trò quan trọng đối với tính khả thi và khả năng chi trả của bảng. Những cân nhắc bao gồm:

a) Sự sẵn có của vật liệu:Trình tự xếp chồng được chọn phải phù hợp với tính sẵn có của vật liệu và khả năng tương thích của chúng với quy trình sản xuất PCB đã chọn.

b) Số lớp và độ phức tạp:Trình tự xếp chồng phải được thiết kế trong giới hạn của quy trình sản xuất PCB đã chọn, có tính đến các yếu tố như số lớp, tỷ lệ khung hình khoan và độ chính xác căn chỉnh.

c) Tối ưu hóa chi phí:Trình tự xếp chồng sẽ tối ưu hóa việc sử dụng vật liệu và giảm độ phức tạp trong sản xuất mà không ảnh hưởng đến hiệu suất và độ tin cậy cần thiết. Nó phải nhằm mục đích giảm thiểu chi phí liên quan đến lãng phí vật liệu, độ phức tạp của quy trình và lắp ráp.

2.4 Căn chỉnh lớp và nhiễu xuyên âm tín hiệu:

Trình tự xếp chồng sẽ giải quyết các vấn đề liên kết lớp và giảm thiểu nhiễu xuyên âm tín hiệu có thể tác động tiêu cực đến tính toàn vẹn của tín hiệu. Những cân nhắc quan trọng bao gồm:

a) Xếp chồng đối xứng:Việc xếp chồng đối xứng các lớp tín hiệu giữa lớp nguồn và lớp đất giúp giảm thiểu sự ghép nối và giảm nhiễu xuyên âm.

b) Định tuyến cặp vi sai:Trình tự xếp chồng sẽ cho phép các lớp tín hiệu được căn chỉnh chính xác để định tuyến hiệu quả các tín hiệu vi sai tốc độ cao. Điều này giúp duy trì tính toàn vẹn của tín hiệu và giảm thiểu nhiễu xuyên âm.

c) Tách tín hiệu:Trình tự xếp chồng nên xem xét việc tách các tín hiệu tương tự và kỹ thuật số nhạy cảm để giảm nhiễu xuyên âm và nhiễu.

2.5 Kiểm soát trở kháng và tích hợp RF/vi sóng:

Đối với các ứng dụng RF/vi sóng, trình tự xếp chồng là rất quan trọng để đạt được khả năng tích hợp và kiểm soát trở kháng thích hợp. Những cân nhắc chính bao gồm:

a) Trở kháng điều khiển:Trình tự xếp chồng phải cho phép thiết kế trở kháng được kiểm soát, có tính đến các yếu tố như chiều rộng vết, độ dày điện môi và cách sắp xếp lớp. Điều này đảm bảo việc truyền tín hiệu chính xác và kết hợp trở kháng cho tín hiệu RF/vi sóng.

b) Vị trí lớp tín hiệu:Tín hiệu RF/vi sóng phải được đặt một cách chiến lược gần lớp bên ngoài để giảm thiểu nhiễu từ các tín hiệu khác và giúp truyền tín hiệu tốt hơn.

c) Che chắn RF:Trình tự xếp chồng phải bao gồm việc bố trí thích hợp các lớp đất và lớp che chắn để cách ly và bảo vệ tín hiệu RF/vi sóng khỏi bị nhiễu.

3. Phương thức kết nối giữa các lớp

3.1 Lỗ xuyên, lỗ mù và lỗ chôn:

Vias được sử dụng rộng rãi trong thiết kế bảng mạch in (PCB) như một phương tiện kết nối các lớp khác nhau. Chúng được khoan lỗ xuyên qua tất cả các lớp PCB và được mạ để đảm bảo tính liên tục về điện. Thông qua các lỗ cung cấp một kết nối điện mạnh mẽ và tương đối dễ dàng để thực hiện và sửa chữa. Tuy nhiên, chúng yêu cầu kích thước mũi khoan lớn hơn, chiếm không gian quý giá trên PCB và hạn chế các tùy chọn định tuyến.

Vias mù và chôn là các phương pháp kết nối giữa các lớp thay thế mang lại lợi thế trong việc sử dụng không gian và định tuyến linh hoạt.

Các lỗ mù được khoan từ bề mặt PCB và kết thúc ở các lớp bên trong mà không đi qua tất cả các lớp. Chúng cho phép kết nối giữa các lớp liền kề trong khi không làm ảnh hưởng đến các lớp sâu hơn. Điều này cho phép sử dụng không gian bảng hiệu quả hơn và giảm số lượng lỗ khoan. Mặt khác, các lỗ chôn là các lỗ được bao bọc hoàn toàn bên trong các lớp bên trong của PCB và không mở rộng ra các lớp bên ngoài. Chúng cung cấp các kết nối giữa các lớp bên trong mà không ảnh hưởng đến các lớp bên ngoài. Vias chôn có lợi thế tiết kiệm không gian lớn hơn so với lỗ xuyên và vias mù vì chúng không chiếm bất kỳ không gian nào ở lớp bên ngoài.

Việc lựa chọn lỗ xuyên, lỗ mù và lỗ chôn tùy thuộc vào yêu cầu cụ thể của thiết kế PCB. Các lỗ thông thường được sử dụng trong các thiết kế đơn giản hơn hoặc trong đó độ bền và khả năng sửa chữa là mối quan tâm hàng đầu. Trong các thiết kế mật độ cao trong đó không gian là yếu tố quan trọng, chẳng hạn như thiết bị cầm tay, điện thoại thông minh và máy tính xách tay, các vias mù và chôn lấp được ưu tiên hơn.

3.2 Micropore vàCông nghệ HDI:

Microvias là các lỗ có đường kính nhỏ (thường nhỏ hơn 150 micron) cung cấp các kết nối giữa các lớp mật độ cao trong PCB. Chúng mang lại những lợi thế đáng kể trong việc thu nhỏ, tính toàn vẹn tín hiệu và tính linh hoạt định tuyến.

Microvias có thể được chia thành hai loại: microvias xuyên lỗ và microvias mù. Microvias được chế tạo bằng cách khoan các lỗ từ bề mặt trên cùng của PCB và kéo dài qua tất cả các lớp. Microvias mù, như tên cho thấy, chỉ mở rộng đến các lớp bên trong cụ thể và không thâm nhập vào tất cả các lớp.

Kết nối mật độ cao (HDI) là công nghệ sử dụng microvias và kỹ thuật sản xuất tiên tiến để đạt được mật độ và hiệu suất mạch cao hơn. Công nghệ HDI cho phép bố trí các thành phần nhỏ hơn và định tuyến chặt chẽ hơn, dẫn đến hệ số dạng nhỏ hơn và tính toàn vẹn tín hiệu cao hơn. Công nghệ HDI mang lại một số lợi thế so với công nghệ PCB truyền thống về khả năng thu nhỏ, truyền tín hiệu được cải thiện, giảm méo tín hiệu và chức năng nâng cao. Nó cho phép thiết kế nhiều lớp với nhiều microvia, do đó rút ngắn độ dài kết nối và giảm điện dung và điện cảm ký sinh.

Công nghệ HDI cũng cho phép sử dụng các vật liệu tiên tiến như tấm mỏng tần số cao và lớp điện môi mỏng, rất quan trọng đối với các ứng dụng RF/vi sóng. Nó cung cấp khả năng kiểm soát trở kháng tốt hơn, giảm mất tín hiệu và đảm bảo truyền tín hiệu tốc độ cao đáng tin cậy.

3.3 Vật liệu và quy trình kết nối giữa các lớp:

Việc lựa chọn vật liệu và kỹ thuật kết nối giữa các lớp là rất quan trọng để đảm bảo hiệu suất điện tốt, độ tin cậy cơ học và khả năng sản xuất của PCB. Một số vật liệu và kỹ thuật kết nối giữa các lớp thường được sử dụng là:

a) Đồng:Đồng được sử dụng rộng rãi trong các lớp dẫn điện và các lớp PCB do tính dẫn điện và khả năng hàn tuyệt vời của nó. Nó thường được mạ vào lỗ để cung cấp kết nối điện đáng tin cậy.

b) Hàn:Các kỹ thuật hàn, chẳng hạn như hàn sóng hoặc hàn nóng chảy lại, thường được sử dụng để tạo kết nối điện giữa các lỗ xuyên qua trên PCB và các thành phần khác. Bôi kem hàn vào lỗ thông và truyền nhiệt để làm nóng chảy chất hàn và tạo thành kết nối đáng tin cậy.

c) Mạ điện:Các kỹ thuật mạ điện như mạ đồng điện phân hoặc đồng điện phân được sử dụng để mạ vias nhằm tăng cường độ dẫn điện và đảm bảo kết nối điện tốt.

d) Liên kết:Các kỹ thuật liên kết, chẳng hạn như liên kết dính hoặc liên kết nén nhiệt, được sử dụng để nối các cấu trúc lớp lại với nhau và tạo ra các kết nối đáng tin cậy.

e) Vật liệu cách điện:Việc lựa chọn vật liệu điện môi để xếp chồng PCB là rất quan trọng đối với các kết nối giữa các lớp. Các tấm tần số cao như tấm FR-4 hoặc Rogers thường được sử dụng để đảm bảo tính toàn vẹn tín hiệu tốt và giảm thiểu mất tín hiệu.

3.4 Thiết kế mặt cắt ngang và ý nghĩa:

Thiết kế mặt cắt ngang của ngăn xếp PCB xác định các đặc tính điện và cơ của các kết nối giữa các lớp. Những cân nhắc chính cho thiết kế mặt cắt ngang bao gồm:

a) Sắp xếp lớp:Việc sắp xếp các mặt phẳng tín hiệu, nguồn và mặt đất trong ngăn xếp PCB ảnh hưởng đến tính toàn vẹn của tín hiệu, tính toàn vẹn của nguồn và nhiễu điện từ (EMI). Vị trí và căn chỉnh thích hợp của các lớp tín hiệu với mặt phẳng nguồn và mặt đất giúp giảm thiểu sự ghép nhiễu và đảm bảo đường dẫn trở lại có độ tự cảm thấp.

b) Điều khiển trở kháng:Thiết kế mặt cắt phải tính đến các yêu cầu trở kháng được kiểm soát, đặc biệt đối với tín hiệu số hoặc tín hiệu RF/vi sóng tốc độ cao. Điều này liên quan đến việc lựa chọn thích hợp vật liệu điện môi và độ dày để đạt được trở kháng đặc tính mong muốn.

c) Quản lý nhiệt:Thiết kế mặt cắt ngang cần xem xét khả năng tản nhiệt và quản lý nhiệt hiệu quả. Vị trí thích hợp của nguồn điện và mặt đất, đường dẫn nhiệt và các bộ phận có cơ chế làm mát (chẳng hạn như bộ tản nhiệt) giúp tản nhiệt và duy trì nhiệt độ vận hành tối ưu.

d) Độ tin cậy cơ học:Thiết kế mặt cắt nên xem xét độ tin cậy cơ học, đặc biệt là trong các ứng dụng có thể phải chịu chu kỳ nhiệt hoặc ứng suất cơ học. Việc lựa chọn vật liệu, kỹ thuật liên kết và cấu hình xếp chồng phù hợp giúp đảm bảo tính toàn vẹn về cấu trúc và độ bền của PCB.

4. Hướng dẫn thiết kế cho PCB 16 lớp

4.1 Phân bổ và phân phối lớp:

Khi thiết kế bảng mạch 16 lớp, điều quan trọng là phải phân bổ và phân bổ cẩn thận các lớp để tối ưu hóa hiệu suất và tính toàn vẹn của tín hiệu. Dưới đây là một số nguyên tắc để phân bổ cấp bậc

và phân phối:

Xác định số lớp tín hiệu cần thiết:

Hãy xem xét độ phức tạp của thiết kế mạch và số lượng tín hiệu cần được định tuyến. Phân bổ đủ các lớp tín hiệu để đáp ứng tất cả các tín hiệu cần thiết, đảm bảo đủ không gian định tuyến và tránh sử dụng quá nhiều tín hiệu.sự tắc nghẽn. Chỉ định mặt đất và mặt phẳng điện:

Gán ít nhất hai lớp bên trong cho mặt phẳng nối đất và cấp nguồn. Mặt đất giúp cung cấp tham chiếu ổn định cho tín hiệu và giảm thiểu nhiễu điện từ (EMI). Mặt phẳng nguồn cung cấp mạng phân phối điện có trở kháng thấp giúp giảm thiểu sụt áp.

Tách các lớp tín hiệu nhạy cảm:

Tùy thuộc vào ứng dụng, có thể cần phải tách các lớp tín hiệu nhạy cảm hoặc tốc độ cao khỏi các lớp nhiễu hoặc công suất cao để ngăn chặn nhiễu và nhiễu xuyên âm. Điều này có thể được thực hiện bằng cách đặt các mặt đất hoặc nguồn điện chuyên dụng giữa chúng hoặc sử dụng các lớp cách ly.

Phân bố đều các lớp tín hiệu:

Phân phối đồng đều các lớp tín hiệu trong toàn bộ bảng xếp chồng để giảm thiểu sự ghép nối giữa các tín hiệu lân cận và duy trì tính toàn vẹn của tín hiệu. Tránh đặt các lớp tín hiệu cạnh nhau trong cùng một khu vực xếp chồng để giảm thiểu nhiễu xuyên âm giữa các lớp.

Hãy xem xét các tín hiệu tần số cao:

Nếu thiết kế của bạn chứa tín hiệu tần số cao, hãy cân nhắc việc đặt các lớp tín hiệu tần số cao gần các lớp bên ngoài hơn để giảm thiểu hiệu ứng đường truyền và giảm độ trễ truyền sóng.

4.2 Định tuyến và định tuyến tín hiệu:

Thiết kế định tuyến và theo dõi tín hiệu là rất quan trọng để đảm bảo tính toàn vẹn tín hiệu thích hợp và giảm thiểu nhiễu. Dưới đây là một số hướng dẫn về cách bố trí và định tuyến tín hiệu trên bảng mạch 16 lớp:

Sử dụng dấu vết rộng hơn cho tín hiệu dòng điện cao:

Đối với các tín hiệu mang dòng điện cao, chẳng hạn như kết nối nguồn và nối đất, hãy sử dụng đường dẫn rộng hơn để giảm thiểu điện trở và sụt áp.

Trở kháng phù hợp cho tín hiệu tốc độ cao:

Đối với tín hiệu tốc độ cao, hãy đảm bảo rằng trở kháng vết phù hợp với trở kháng đặc tính của đường truyền để tránh phản xạ và suy giảm tín hiệu. Sử dụng các kỹ thuật thiết kế trở kháng được kiểm soát và tính toán độ rộng vết chính xác.

Giảm thiểu độ dài dấu vết và điểm giao nhau:

Giữ độ dài vết càng ngắn càng tốt và giảm số lượng điểm giao nhau để giảm điện dung, điện cảm và nhiễu ký sinh. Tối ưu hóa vị trí thành phần và sử dụng các lớp định tuyến chuyên dụng để tránh các dấu vết dài và phức tạp.

Tách tín hiệu tốc độ cao và tốc độ thấp:

Tách riêng tín hiệu tốc độ cao và tốc độ thấp để giảm thiểu tác động của nhiễu lên tín hiệu tốc độ cao. Đặt tín hiệu tốc độ cao trên các lớp tín hiệu chuyên dụng và tránh xa các thành phần có công suất cao hoặc nhiễu.

Sử dụng cặp vi sai cho tín hiệu tốc độ cao:

Để giảm thiểu nhiễu và duy trì tính toàn vẹn tín hiệu cho tín hiệu vi sai tốc độ cao, hãy sử dụng kỹ thuật định tuyến cặp vi sai. Giữ trở kháng và độ dài của các cặp vi sai phù hợp để tránh hiện tượng lệch tín hiệu và nhiễu xuyên âm.

4.3 Phân bố lớp đất và lớp điện:

Việc phân bổ hợp lý các mặt đất và nguồn điện là rất quan trọng để đạt được tính toàn vẹn nguồn điện tốt và giảm nhiễu điện từ. Dưới đây là một số hướng dẫn về bài tập mặt đất và mặt phẳng nguồn trên bảng mạch 16 lớp:

Phân bổ mặt đất và mặt phẳng điện chuyên dụng:

Phân bổ ít nhất hai lớp bên trong cho mặt đất và mặt phẳng điện chuyên dụng. Điều này giúp giảm thiểu vòng lặp trên mặt đất, giảm EMI và cung cấp đường dẫn trở lại có trở kháng thấp cho tín hiệu tần số cao.

Các mặt phẳng mặt đất kỹ thuật số và tương tự riêng biệt:

Nếu thiết kế có các phần kỹ thuật số và analog thì nên có mặt phẳng nền riêng cho từng phần. Điều này giúp giảm thiểu sự ghép nhiễu giữa các phần kỹ thuật số và analog và cải thiện tính toàn vẹn của tín hiệu.

Đặt mặt đất và mặt phẳng nguồn gần mặt phẳng tín hiệu:

Đặt mặt đất và mặt phẳng nguồn gần với mặt phẳng tín hiệu mà chúng cung cấp để giảm thiểu diện tích vòng lặp và giảm nhiễu.

Sử dụng nhiều vias cho các mặt phẳng điện:

Sử dụng nhiều vias để kết nối các mặt phẳng nguồn để phân phối điện đồng đều và giảm trở kháng mặt phẳng nguồn. Điều này giúp giảm thiểu sụt áp nguồn và cải thiện tính toàn vẹn của nguồn điện.

Tránh cổ hẹp trong máy bay điện:

Tránh các cổ hẹp trong mặt phẳng nguồn vì chúng có thể gây ra hiện tượng dồn dòng và tăng điện trở, dẫn đến sụt áp và làm kém hiệu quả của mặt phẳng nguồn. Sử dụng kết nối mạnh mẽ giữa các khu vực mặt phẳng điện khác nhau.

4.4 Tấm tản nhiệt và thông qua vị trí:

Vị trí thích hợp của miếng đệm nhiệt và lỗ thông hơi là rất quan trọng để tản nhiệt hiệu quả và ngăn ngừa các bộ phận quá nóng. Dưới đây là một số hướng dẫn về miếng đệm nhiệt và cách đặt trên bảng mạch 16 lớp:

Đặt tấm tản nhiệt bên dưới các bộ phận sinh nhiệt:

Xác định thành phần tạo nhiệt (chẳng hạn như bộ khuếch đại công suất hoặc IC công suất cao) và đặt tấm tản nhiệt ngay bên dưới nó. Những miếng đệm nhiệt này cung cấp một đường dẫn nhiệt trực tiếp để truyền nhiệt đến lớp nhiệt bên trong.

Sử dụng nhiều vias nhiệt để tản nhiệt:

Sử dụng nhiều vias nhiệt để kết nối lớp nhiệt và lớp bên ngoài để mang lại khả năng tản nhiệt hiệu quả. Các via này có thể được đặt theo mô hình so le xung quanh tấm tản nhiệt để đạt được sự phân bổ nhiệt đều.

Xem xét trở kháng nhiệt và xếp chồng lớp:

Khi thiết kế các via tản nhiệt, hãy xem xét trở kháng nhiệt của vật liệu bo mạch và việc xếp chồng các lớp. Tối ưu hóa thông qua kích thước và khoảng cách để giảm thiểu lực cản nhiệt và tối đa hóa khả năng tản nhiệt.

4.5 Vị trí thành phần và tính toàn vẹn tín hiệu:

Vị trí thành phần thích hợp là rất quan trọng để duy trì tính toàn vẹn của tín hiệu và giảm thiểu nhiễu. Dưới đây là một số hướng dẫn để đặt các thành phần trên bảng mạch 16 lớp:

Các thành phần liên quan đến nhóm:

Nhóm các thành phần liên quan là một phần của cùng một hệ thống con hoặc có tương tác điện mạnh. Điều này làm giảm độ dài dấu vết và giảm thiểu sự suy giảm tín hiệu.

Giữ các bộ phận tốc độ cao ở gần:

Đặt các bộ phận tốc độ cao, chẳng hạn như bộ dao động tần số cao hoặc bộ vi điều khiển, gần nhau để giảm thiểu độ dài dấu vết và đảm bảo tính toàn vẹn tín hiệu thích hợp.

Giảm thiểu độ dài vết của các tín hiệu quan trọng:

Giảm thiểu độ dài vết của các tín hiệu quan trọng để giảm độ trễ truyền và suy giảm tín hiệu. Đặt các thành phần này càng gần càng tốt.

Tách biệt các thành phần nhạy cảm:

Tách riêng các thành phần nhạy cảm với nhiễu, chẳng hạn như các thành phần analog hoặc cảm biến mức thấp, khỏi các thành phần có công suất cao hoặc nhiễu để giảm thiểu nhiễu và duy trì tính toàn vẹn của tín hiệu.

Xem xét việc tách tụ điện:

Đặt các tụ tách càng gần các chân nguồn của từng bộ phận càng tốt để cung cấp nguồn điện sạch và giảm thiểu dao động điện áp. Những tụ điện này giúp ổn định nguồn điện và giảm nhiễu.

5. Công cụ mô phỏng và phân tích cho thiết kế xếp chồng

5.1 Phần mềm mô phỏng và mô phỏng 3D:

Phần mềm mô phỏng và tạo mô hình 3D là một công cụ quan trọng để thiết kế xếp chồng vì nó cho phép các nhà thiết kế tạo ra các biểu diễn ảo của các ngăn xếp PCB. Phần mềm có thể trực quan hóa các lớp, thành phần và tương tác vật lý của chúng. Bằng cách mô phỏng việc xếp chồng, các nhà thiết kế có thể xác định các vấn đề tiềm ẩn như nhiễu xuyên âm tín hiệu, EMI và các hạn chế cơ học. Nó cũng giúp xác minh việc sắp xếp các thành phần và tối ưu hóa thiết kế PCB tổng thể.

5.2 Công cụ phân tích tính toàn vẹn tín hiệu:

Các công cụ phân tích tính toàn vẹn tín hiệu rất quan trọng để phân tích và tối ưu hóa hiệu suất điện của các bộ xếp chồng PCB. Những công cụ này sử dụng thuật toán toán học để mô phỏng và phân tích hành vi tín hiệu, bao gồm kiểm soát trở kháng, phản xạ tín hiệu và ghép nhiễu. Bằng cách thực hiện mô phỏng và phân tích, các nhà thiết kế có thể xác định sớm các vấn đề tiềm ẩn về tính toàn vẹn của tín hiệu trong quá trình thiết kế và thực hiện các điều chỉnh cần thiết để đảm bảo truyền tín hiệu đáng tin cậy.

5.3 Dụng cụ phân tích nhiệt:

Các công cụ phân tích nhiệt đóng vai trò quan trọng trong thiết kế xếp chồng bằng cách phân tích và tối ưu hóa việc quản lý nhiệt của PCB. Những công cụ này mô phỏng sự tản nhiệt và phân bổ nhiệt độ trong mỗi lớp của ngăn xếp. Bằng cách mô hình hóa chính xác đường dẫn tiêu tán năng lượng và truyền nhiệt, các nhà thiết kế có thể xác định các điểm nóng, tối ưu hóa vị trí của các lớp đồng và đường dẫn nhiệt, đồng thời đảm bảo làm mát thích hợp các bộ phận quan trọng.

5.4 Thiết kế cho khả năng sản xuất:

Thiết kế cho khả năng sản xuất là một khía cạnh quan trọng của thiết kế xếp chồng. Có sẵn nhiều công cụ phần mềm khác nhau có thể giúp đảm bảo rằng khối đã chọn có thể được sản xuất một cách hiệu quả. Những công cụ này cung cấp phản hồi về tính khả thi của việc đạt được mức xếp chồng mong muốn, có tính đến các yếu tố như tính sẵn có của vật liệu, độ dày lớp, quy trình sản xuất và chi phí sản xuất. Chúng giúp các nhà thiết kế đưa ra quyết định sáng suốt nhằm tối ưu hóa việc xếp chồng nhằm đơn giản hóa quá trình sản xuất, giảm nguy cơ chậm trễ và tăng năng suất.

6.Quy trình thiết kế từng bước cho PCB 16 lớp

6.1 Thu thập yêu cầu ban đầu:

Ở bước này, thu thập tất cả các yêu cầu cần thiết cho thiết kế PCB 16 lớp. Hiểu chức năng của PCB, hiệu suất điện cần thiết, các ràng buộc cơ học và bất kỳ nguyên tắc hoặc tiêu chuẩn thiết kế cụ thể nào cần phải tuân theo.

6.2 Phân bổ và sắp xếp thành phần:

Theo yêu cầu, phân bổ các thành phần trên PCB và xác định cách sắp xếp của chúng. Xem xét các yếu tố như tính toàn vẹn của tín hiệu, các cân nhắc về nhiệt và các ràng buộc cơ học. Nhóm các thành phần dựa trên đặc tính điện và đặt chúng một cách chiến lược trên bo mạch để giảm thiểu nhiễu và tối ưu hóa luồng tín hiệu.

6.3 Thiết kế xếp chồng và phân bố lớp:

Xác định thiết kế xếp chồng cho PCB 16 lớp. Hãy xem xét các yếu tố như hằng số điện môi, độ dẫn nhiệt và chi phí để lựa chọn vật liệu phù hợp. Chỉ định tín hiệu, nguồn và mặt phẳng mặt đất theo yêu cầu về điện. Đặt mặt đất và mặt phẳng nguồn đối xứng nhau để đảm bảo ngăn xếp cân bằng và cải thiện tính toàn vẹn của tín hiệu.

6.4 Định tuyến tín hiệu và tối ưu hóa định tuyến:

Ở bước này, các dấu vết tín hiệu được định tuyến giữa các thành phần để đảm bảo kiểm soát trở kháng thích hợp, tính toàn vẹn của tín hiệu và giảm thiểu nhiễu xuyên âm tín hiệu. Tối ưu hóa định tuyến để giảm thiểu độ dài của tín hiệu quan trọng, tránh vượt qua các dấu vết nhạy cảm và duy trì sự tách biệt giữa tín hiệu tốc độ cao và tốc độ thấp. Sử dụng các cặp vi sai và kỹ thuật định tuyến trở kháng được kiểm soát khi cần thiết.

6.5 Kết nối giữa các lớp và thông qua vị trí:

Lập kế hoạch vị trí kết nối vias giữa các lớp. Xác định loại thông qua phù hợp, chẳng hạn như thông qua lỗ hoặc lỗ mù, dựa trên sự chuyển đổi lớp và kết nối thành phần. Tối ưu hóa thông qua bố cục để giảm thiểu phản xạ tín hiệu, gián đoạn trở kháng và duy trì sự phân bố đồng đều trên PCB.

6.6 Xác minh và mô phỏng thiết kế cuối cùng:

Trước khi sản xuất, việc xác minh và mô phỏng thiết kế cuối cùng sẽ được thực hiện. Sử dụng các công cụ mô phỏng để phân tích thiết kế PCB về tính toàn vẹn tín hiệu, tính toàn vẹn nguồn điện, đặc tính nhiệt và khả năng sản xuất. Xác minh thiết kế dựa trên các yêu cầu ban đầu và thực hiện các điều chỉnh cần thiết để tối ưu hóa hiệu suất và đảm bảo khả năng sản xuất.

Cộng tác và liên lạc với các bên liên quan khác như kỹ sư điện, kỹ sư cơ khí và nhóm sản xuất trong suốt quá trình thiết kế để đảm bảo đáp ứng mọi yêu cầu và các vấn đề tiềm ẩn được giải quyết. Thường xuyên xem xét và lặp lại các thiết kế để kết hợp phản hồi và cải tiến.

7. Thực tiễn tốt nhất và nghiên cứu trường hợp trong ngành

7.1 Các trường hợp thiết kế PCB 16 lớp thành công:

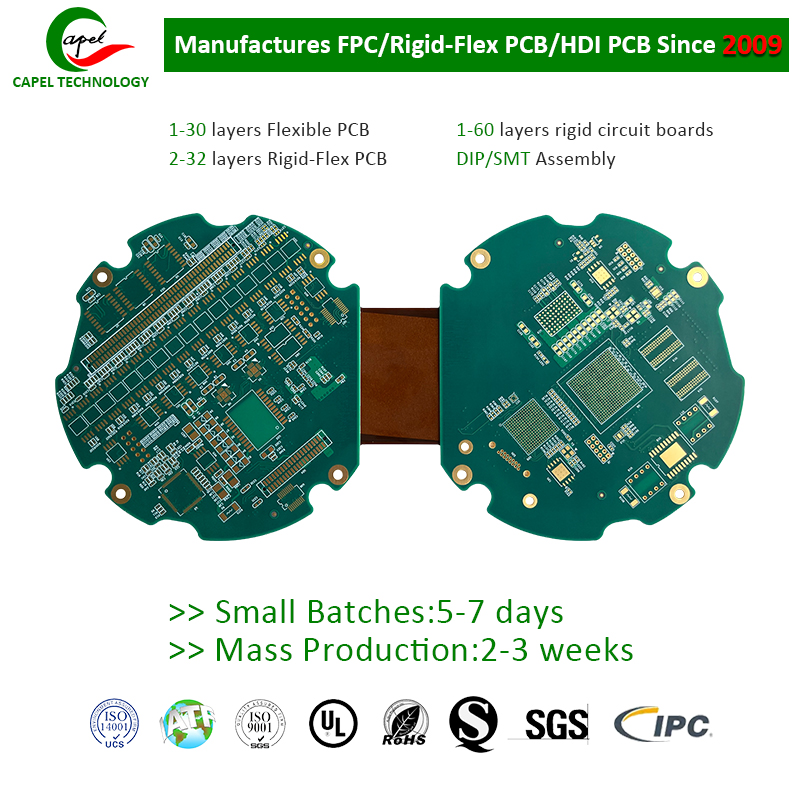

Nghiên cứu trường hợp 1:Công ty TNHH Công nghệ Capel Thâm Quyến đã thiết kế thành công PCB 16 lớp cho thiết bị mạng tốc độ cao. Bằng cách xem xét cẩn thận tính toàn vẹn của tín hiệu và phân phối điện năng, chúng đạt được hiệu suất vượt trội và giảm thiểu nhiễu điện từ. Chìa khóa thành công của họ là thiết kế xếp chồng được tối ưu hóa hoàn toàn bằng công nghệ định tuyến trở kháng được kiểm soát.

Nghiên cứu trường hợp 2:Công ty TNHH Công nghệ Capel Thâm Quyến đã thiết kế PCB 16 lớp cho một thiết bị y tế phức tạp. Bằng cách sử dụng kết hợp các bộ phận gắn trên bề mặt và xuyên lỗ, họ đã đạt được thiết kế nhỏ gọn nhưng mạnh mẽ. Vị trí thành phần cẩn thận và định tuyến hiệu quả đảm bảo tính toàn vẹn và độ tin cậy tín hiệu tuyệt vời.

7.2 Học từ thất bại và tránh cạm bẫy:

Nghiên cứu điển hình 1:Một số nhà sản xuất pcb gặp phải vấn đề về tính toàn vẹn tín hiệu trong thiết kế PCB 16 lớp của thiết bị truyền thông. Nguyên nhân thất bại là do không xem xét đầy đủ việc kiểm soát trở kháng và thiếu sự phân bố mặt đất thích hợp. Bài học rút ra là phân tích cẩn thận các yêu cầu về tính toàn vẹn của tín hiệu và thực thi các nguyên tắc thiết kế kiểm soát trở kháng nghiêm ngặt.

Nghiên cứu trường hợp 2:Một số nhà sản xuất pcb phải đối mặt với những thách thức trong sản xuất với PCB 16 lớp do độ phức tạp trong thiết kế. Việc lạm dụng các via mù và các bộ phận được đóng gói dày đặc dẫn đến khó khăn trong sản xuất và lắp ráp. Bài học rút ra là đạt được sự cân bằng giữa độ phức tạp của thiết kế và khả năng sản xuất dựa trên khả năng của nhà sản xuất PCB đã chọn.

Để tránh những cạm bẫy và cạm bẫy trong thiết kế PCB 16 lớp, điều quan trọng là phải:

a.Hiểu rõ các yêu cầu và ràng buộc của thiết kế.

b.Cấu hình xếp chồng giúp tối ưu hóa tính toàn vẹn tín hiệu và phân phối điện năng. c.Phân phối và sắp xếp cẩn thận các bộ phận để tối ưu hóa hiệu suất và đơn giản hóa quá trình sản xuất.

d.Đảm bảo các kỹ thuật định tuyến thích hợp, chẳng hạn như kiểm soát trở kháng và tránh sử dụng quá nhiều vias mù.

e.Cộng tác và giao tiếp hiệu quả với tất cả các bên liên quan trong quá trình thiết kế, bao gồm các kỹ sư điện, cơ khí và nhóm sản xuất.

f.Thực hiện xác minh và mô phỏng thiết kế toàn diện để xác định và khắc phục các vấn đề tiềm ẩn trước khi sản xuất.

Thời gian đăng: 26-09-2023

Mặt sau